AECU-3635 (and Ed.)

UNIVERSITY OF ILLINOIS GRADUATE COLLEGE DIGITAL COMPUTER LABORATORY

MASTER

**REPORT NO. 80**

# ON THE DESIGN OF A VERY HIGH-SPEED COMPUTER

OCTOBER 1957

SECOND EDITION

(Revised in Part April 1958)

PONOT

This work was supported in part by the Atomic Energy Commission and the Office of Naval Research under AEC Contract AT(11-1)-415

# DISCLAIMER

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency Thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

# DISCLAIMER

Portions of this document may be illegible in electronic image products. Images are produced from the best available original document.

AEC4-3635

#### UNIVERSITY OF ILLINOIS

GRADUATE COLLEGE

DIGITAL COMPUTER LABORATORY

URBANA, ILLINOIS

REPORT NO. 80

## ON THE DESIGN OF A VERY HIGH-SPEED COMPUTER

October 1957

Second Edition (Revised in Part - April 1958)

LEGAL NOTICE sored work. Neither the United of the Commission: mplied, with respect to the accu-d in this report, or that the use This report was pre nt of Government sponsored States. tes, nor the Commission, nor an A. Makes any warranty or repr on, expressed or impl racy, completeness, or usef iness of the information contai y information, apparatus, method, or process disclosed in this report may not infringe with respect to the use of, or for m the b respect to use use an method, or process disclosed in this rep maching on behalf of the Commission" ission, or employee of such contractor e Commission, or employee of such co o, say information purchant to his employ the use contractor. process disclosed in this report. an of such contractor, to the extent that ch employee or co disse disseminates, or provides access to, any information pursuant with the Commission, or his employment with such contractor.

This work was supported in part by the Atomic Energy Commission and the Office of Naval Research

under AEC Contract AT(11-1)-415

#### PREFACE TO FIRST EDITION

This report summarizes the work of the Digital Computer Laboratory of the University of Illinois on a study of the feasibility of constructing a computer about one hundred times faster than present computers such as Illiac using presently available components and techniques.

Some promising designs and design features considered by the Digital Computer Laboratory are either not discussed in this report or are relegated to somewhat subordinate places in the report because they involve equipment which in the opinion of this Laboratory has a low probability of being built so as to have acceptable reliability with presently available components and techniques.

The first part of this report, Chapters 1, 2 and 3, deals with general features of the proposed computer and postulates the existence of various components and parts. The second part of the report, Chapters 4, 5, 6, 7, and 8, discusses these parts in some detail, beginning with a discussion of the circuits from which the different units of the computer would be built. A summary of the proposed machine's specifications is found on page ix.

The work herein reported contains results of efforts of all the personnel of the Digital Computer Laboratory and some members of the Computation Centre of the University of Toronto. The report was prepared by a committee consisting of D. B. Gillies, R. E. Meagher, D. E. Muller, R. W. McKay(1), J. P. Nash<sup>(2)</sup>, J. E. Robertson and A. H. Taub (Chairman).

The study was supported jointly by the Atomic Energy Commission and the Office of Naval Research under AEC Contract AT(11-1)-415, by the University of Illinois and by the University of Toronto.

October, 1957

#### PREFACE TO SECOND EDITION

The distribution and subsequent mailings of the original printing of this report exhausted the supply (300 copies). This printing is called a second edition because Chapter 4 has been considerably revised. Many new details as well as corrections are contained in this chapter on basic circuits which has been revised by W. J. Poppelbaum. Because circuit times and other circuit constants are affected, numerical data are changed elsewhere. in the text.

A number of other corrections of only a minor nature are included in this edition. The page numbers following Chapter 4 are changed with respect to the first edition.

April, 1958

On the staff of the University of Toronto in residence at the Digital Computer Laboratory, University of Illinois, for the year 1956-57.

Resigned in April 1957.

# CONTENTS

| PREFACE | <b>♀ ↓ ₽ · ● , ●</b> | • • • • • • • • • • • • • • • • • • •                           | i    |

|---------|----------------------|-----------------------------------------------------------------|------|

| SUMMARY | AND CON              | CLUSIONS                                                        | iii  |

| SUMMARY | OF PROP              | OSED MACHINE'S SPECIFICATIONS                                   | ix   |

| Chapter | l.                   | PROBLEMS REQUIRING FAST COMPUTERS                               |      |

|         | 1.1                  | Introduction,                                                   | 1    |

|         | 1.2                  | Hyperbolic and Parabolic Partial Differential Equations .       | -3   |

|         | 1.3                  | Elliptic Partial Differential Equations and Linear<br>Equations | .6   |

| ·       | 1.4                  | Sorting and Meshing Problems                                    | , 7  |

| Chapter | 2.                   | REQUIREMENTS ON A VERY FAST COMPUTER                            |      |

|         | 2.1                  | Memory Capacity Requirements.                                   | 10   |

|         | 2.2                  | The Class of Problems That Can Use Backup Memories              | -14  |

|         | 2.3                  | Speed Requirements on the Memory                                | 18   |

|         | 2.4                  | Numerical Requirements on Word Length                           | - 19 |

|         | 2.5                  | Floating Point Arithmetic                                       | 21   |

| Chapter | 3.                   | PROPOSED ORGANIZATION OF THE COMPUTER                           |      |

|         | 3.1                  | Introduction                                                    | -26  |

|         | 3.2                  | A Design Criterion                                              | 26   |

|         | 3,•3                 | The Speed of a Computer                                         | -28  |

|         | 3.4                  | Red Tape                                                        | . 30 |

|         | 3•5                  | Storage of Addresses                                            | . 31 |

|         | 3.6                  | Storage of Intermediate Results                                 | 31   |

|         | 3•7                  | Access for Instructions and Operands                            | - 32 |

|         | 3.8                  | Summary of Useful Additional Storage                            | 33   |

Chapter 3. (Continued)

| 3.9             | Size of the Core Memory                    | - 34 |

|-----------------|--------------------------------------------|------|

| 3.10            | A Computer with Small Buffer Storage       | - 36 |

| 3.11            | Words and Instructions                     | 37   |

| 3.12            | Controls                                   | - 39 |

| • 3•13          | Example                                    | . 40 |

| 3.14            | The Design of the Two Controls             | .43  |

| 3.15            | Order Code                                 | . 49 |

| 3.16            | Programming Examples                       | 57   |

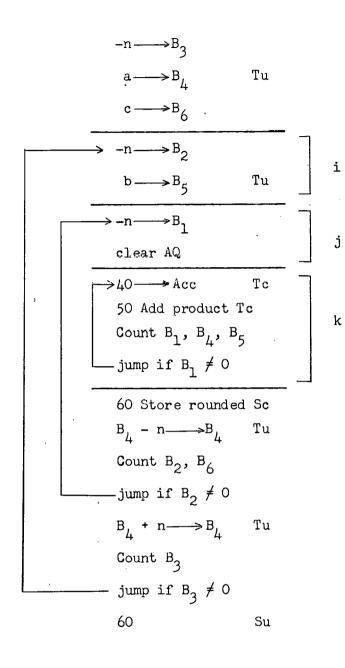

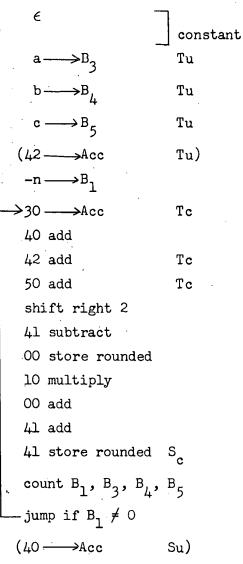

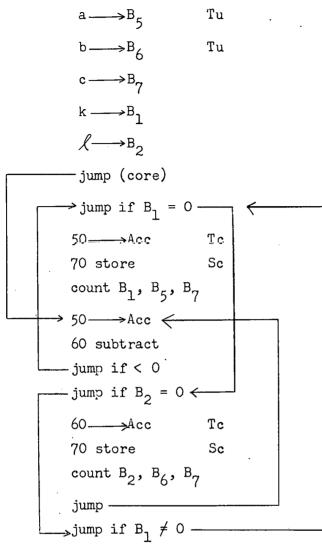

|                 | 3.16.1 The Scalar Product of Two Vectors   | 60   |

|                 | 3.16.2 Evaluation of a Polynomial          | .61  |

|                 | 3.16.3 Continued Fraction.                 | 62   |

|                 | 3.16.4 Reverse the Digits of a Word        | . 63 |

|                 | 3.16.5 Sideways Addition                   | 64   |

| · .             | 3.16.6 Square Root of Y                    | 64   |

| ·               | 3.16.7 Matrix Multiplication               | . 66 |

| Appendix to Cha | pter 3.                                    |      |

| 3.17            | Memory                                     | .68  |

| 3.18            | Execution of Instructions                  | 69   |

| 3.19            | Jump Instructions.                         | : 70 |

| 3.20            | B-Instructions and Block Transfers of Data | 71   |

| 3.21            | Basic Form of Instructions                 | 71   |

| 3.22            | B-Line Instructions                        | , 72 |

| 3.23            | C-Jump Instructions                        | 72   |

iii

Appendix to Chapter 3. (Continued)

|         | 3.24           | Arithmetic Instructions                                                            | 73    |

|---------|----------------|------------------------------------------------------------------------------------|-------|

|         | 3.25           | Input-Output Instructions.                                                         | 73    |

|         | 3.26           | Register Arrangements                                                              | 73    |

|         | 3.27           | Instruction Code                                                                   | . 74  |

|         | 3.28           | Programming Examples                                                               | - 75  |

| Chapter | 4.             | BASIC CIRCUITS                                                                     |       |

|         | 4.1            | Introduction                                                                       | 81    |

|         | 4.2            | Asynchronous vs. Synchronous Operation                                             | 82    |

|         | 4.3            | Direct-Coupling vs. AC-Coupling                                                    | . 84  |

|         | . <b>4 .</b> 4 | Two-Level DC vs. Pulse Representation                                              | .84   |

|         | 4.5            | Transistors vs. Tubes                                                              | 86    |

|         | .4.6           | Reliability and Feasibility of a Transistorized<br>Asynchronous DC-Coupled Machine | .89   |

|         | 4.7            | Tolerances, Critical Levels and Discrimination<br>Levels                           | 90    |

|         | 4.8            | The Last Moving Point Philosophy                                                   | 94    |

|         | 4.9            | Characteristic Times: Switching Time and<br>Operation Time                         | - 97  |

|         | 4.10           | Flow-Gating                                                                        | 1,00  |

|         | 4.11           | Principles of Circuit Analysis and Synthesis                                       | 104   |

|         | 4.12           | Component Specifications                                                           | .106  |

|         | 4.13           | General Remarks about the Next Section                                             | 109   |

|         | 4.14           | NOT Circuit (Class 1).                                                             | 110   |

|         | 4.15           | Level Restorer (Class 1)                                                           | 112   |

|         | 4.16           | OR Circuit (Class 1                                                                | . 113 |

iv

Chapter 4 (Continued)

•.\_.

- 4

|         | 4.17     | AND Circuit (Class 1)                     | ,115  |

|---------|----------|-------------------------------------------|-------|

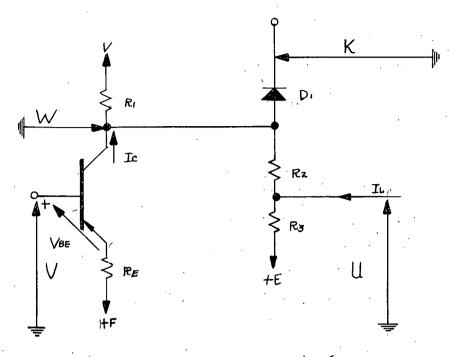

|         | 4.18     | Flow-Gating Flipflop (Class 2)            | 116   |

|         | 4.19     | Schmitt Trigger (Class 3).                | 117   |

|         | .4.20    | Eccles Jordan (Class 3)                   | 118   |

|         | 4.21     | EXCLUSIVE OR (Class 4)                    | 119   |

|         | 4.22     | Driver (Class 4)                          | 120   |

|         | .4.23    | C-Element (Class 4)                       | 122   |

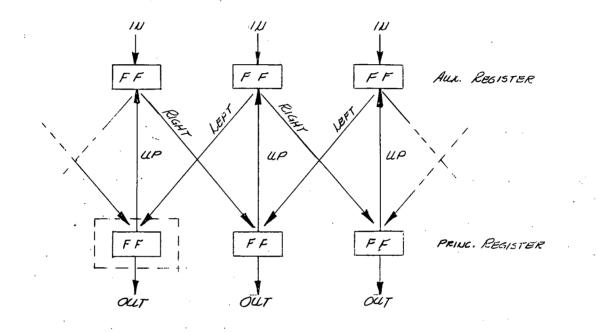

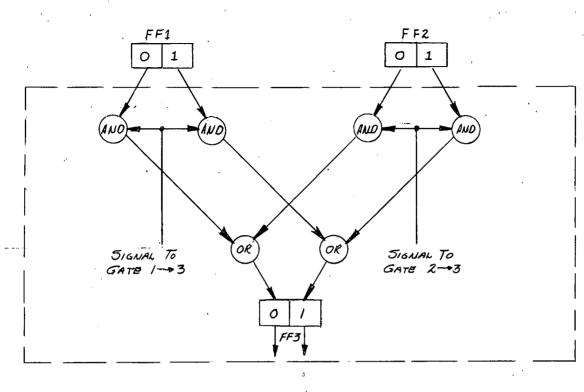

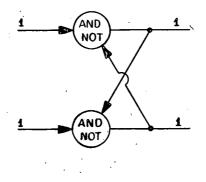

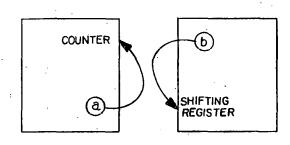

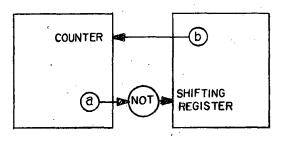

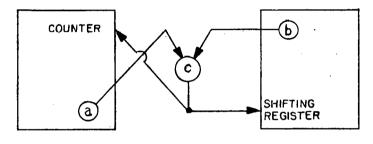

|         | 4.24     | Shifting Registers                        | . 123 |

|         | 4.25     | Summary and Closing Remarks               | 127   |

| Appendi | x to Cha | pter 4                                    | 129   |

| Chapter | 5.       | ASYNCHRONOUS CIRCUITS                     |       |

|         | 5.1      | Introduction                              | 133   |

|         | .5.2     | Speed and Complexity                      | 133   |

|         | ∶5•3     | Design of Asynchronous Circuits           | . 134 |

|         | 5.4      | Location of Malfunctions and their Repair | 136   |

|         | 5.5      | Reliability                               | 136   |

|         | 5.6      | Asynchronous Principles                   | 137   |

|         | 5•7      | Method of Combining Blocks                | 140   |

|         | 5.8      | Method of Simulating Synchronous Circuits | 143   |

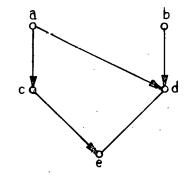

|         | 5.9      | Method of Design from Change Charts       | 147   |

| Chapter |          | MEMORY                                    |       |

|         | 6.1      | Introduction                              | . 150 |

|         | 6.2      | Comparison of Some Types of Memory        | . 151 |

;

v

Chapter 6 (Continued)

|         | 6.3      | Word-Arrangement Memory.                                                   | 154   |

|---------|----------|----------------------------------------------------------------------------|-------|

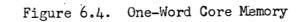

|         | 6.4      | Experimental Results                                                       | . 159 |

| Appendi | x to Cha | pter 6.                                                                    |       |

|         | Possibi  | lity of a Non-Destructive Readout                                          | . 164 |

| Chapter | : 7.     | INPUT, OUTPUT AND AUXILIARY STORAGE                                        |       |

|         | 7.1      | Introduction                                                               | 165   |

|         | 7.2      | Data Rate Characteristics of Scientific and<br>Data Processing Computers   | 167   |

|         | 7•3      | Magnetic Tape Characteristics                                              | 169   |

|         | 7.4      | Magnetic Drum Storage.                                                     | 170   |

|         | 7.5      | Input-Output Requirements for Data Generated<br>or Consumed by Human Users | .171  |

|         | 7.6      | Other Modes of Data Generation or Consumption                              | 172   |

|         | 7.7      | Other Aspects of Machine Balance                                           | 172   |

|         | 7.8      | Summary and Conclusions                                                    | 173   |

| Chapter | . 8      | ARITHMETIC UNIT                                                            |       |

|         | .8.1     | Introduction                                                               | 174   |

|         | 8.2      | Separate Carry Storage in a Binary Arithmetic Unit                         | 180   |

|         | 8.3      | Separate Carry Storage for an Arbitrary Radix                              | 182   |

|         | 8.4      | Binary Subtraction                                                         | 184   |

|         | 8.5      | Carry Assimilation                                                         | 185   |

|         | 8.6      | Analysis of Overflow: Introduction                                         | 187   |

|         | 8.7      | Conventional Overflow Analysis                                             | 188   |

|         | 8.8      | Number Representation with Separate Carry Storage                          | 189   |

|         | 8.9      | Method of Analysis for Overflow.                                           | . 190 |

|         |          |                                                                            |       |

vi

# Chapter 8. (Continued)

| 8.10 | Overflow Detection: Left Shift of One Digital<br>Position                                             | 192  |

|------|-------------------------------------------------------------------------------------------------------|------|

| 8.11 | Overflow Detection: Addition or Subtraction                                                           | 193  |

| 8.12 | Overflow Analysis: Addition or Subtraction Followed by a Right Shift                                  | 195  |

| 8.13 | Overflow Analysis: Left Shift Followed by an Addition or Subtraction Such That the Result is in Range | 196  |

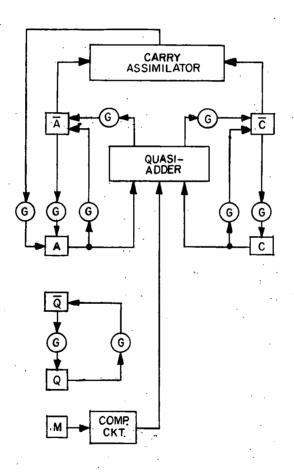

| 8.14 | Multiplication: Introduction                                                                          | 198  |

| 8.15 | The Recoding of the Multiplier                                                                        | 200  |

| 8.16 | The Multiplication Right Shift: Introduction                                                          | 202  |

| 8.17 | The Multiplication Right Shift: The Nature of<br>Corrections if A and Q are of Opposite Sign          | 202  |

| 8.18 | The Multiplication Right Shift: Assimilation of<br>Carries for Digits Transferred from A and C to Q   | 204  |

| 8.19 | Multiplication Overflow                                                                               | -205 |

| 8.20 | Division: Introduction                                                                                | 205  |

| 8.21 | Non-Restoring Division                                                                                | 207  |

| 8.22 | The Standardized Division                                                                             | 209  |

| 8.23 | Division Overflow                                                                                     | 211  |

| 8.24 | Quaternary Operation                                                                                  | 211  |

| 8.25 | Estimates of Operation Times and Hardware Requirements                                                | 212  |

| 8.26 | Interpretation of Speed and Hardware Estimates                                                        | 218  |

| 8.27 | Floating Point Arithmetic                                                                             | 219  |

NOTE: Figures for each chapter have number designations which give first the chapter number, then the point and then the figure number within the chapter.

Footnotes are numbered sequentially beginning with 1 in each chapter separately.

vii

On the basis of the work reported herein the Digital Computer Laboratory of the University of Illinois concludes that it is feasible to construct a very fast digital computer in which the transistor circuits developed in that Laboratory would be used.

The results of two design studies are discussed. One involves a minimum of buffer storage in the form of transistor registers and is outlined in the body of Chapter 3, while the other involves a moderate amount of buffer storage in the form of a small-capacity, high-speed, randomaccess buffer memory and is discussed in the appendix to Chapter 3. The former design is emphasized because it is felt that its equipment requirements can be presently met.

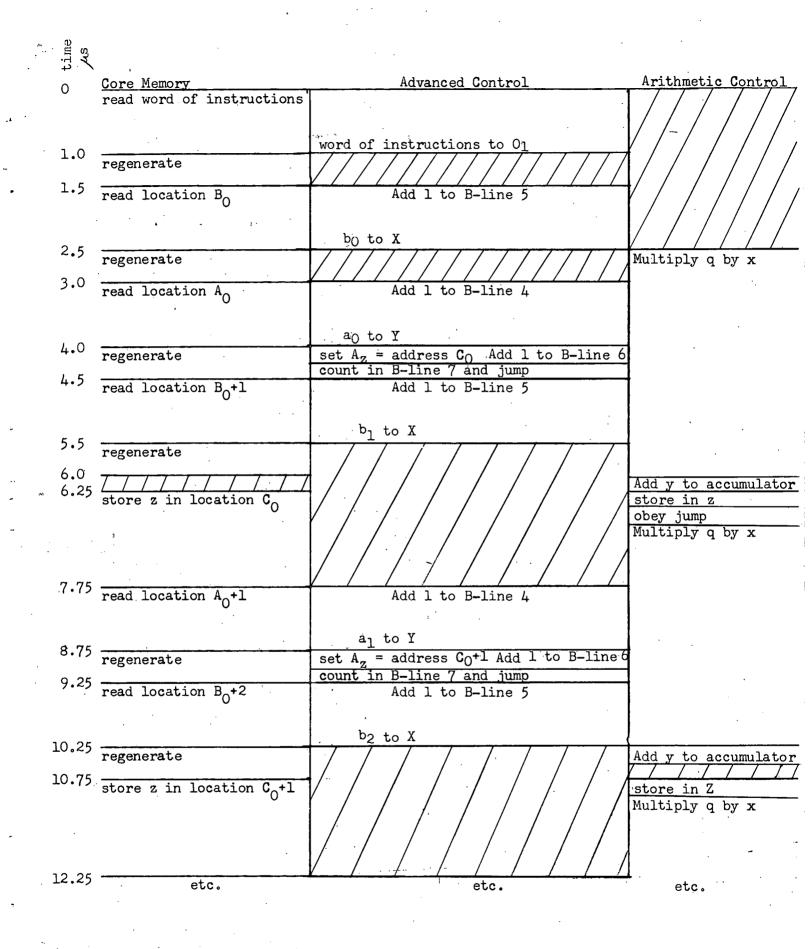

In it, two controls are used, arithmetic control and advanced control, as well as buffer storage for instructions and operands, and by such means various units of the computer are kept in simultaneous operation. For example, B-modifications, memory accesses and complicated arithmetic operations, such as a double-length, add-product instruction, may be performed concurrently. Short but powerful inner loops may be stored outside the memory and acted upon by the control. Many of the gains in speed in the control and arithmetic unit are dependent upon asynchronous operation of these units.

The relative speed of the proposed computer compared to that of existing machines depends upon the problem being solved. For problems dominated by arithmetic operations it is estimated that the proposed computer will be 100 to 200 times faster than computers such as Illiac. For problems dominated by logical and combinatorial operations, this factor of gain in speed will be at least 50.

The proposed computer has a random-access word-arrangement memory of 8192 words of 52 bits each with an access time of 1.5  $\mu s$ .

The arithmetic unit is designed so that the digits of a multiplier are sensed and acted upon in such a way that the use of the adder is reduced. Furthermore, "carry registers" are used in this unit, and carries are assimilated only when necessary. It is expected that the proposed computer will have an average multiplication time between 3.5 and 4  $\mu$ s, addition times (with assimilation) of .3  $\mu$ s, and division times of 7 to 20  $\mu$ s.

The computer, aside from input-output facilities, will contain approximately 15,400 transistors, 34,000 diodes, and 42,000 resistors. The transistors are expected to be Western Electric transistors, type GF-45011.

The basic circuits built from these transistors have operation times of from 5 to  $40^{\circ} \cdot 10^{-9}$  second depending upon the circuit.

viii

#### SUMMARY OF PROPOSED MACHINE'S SPECIFICATIONS

This report covers many aspects of high-speed computing machines. As the study shows, more than one decision concerning machine organization or design is acceptable, and the best decision concerning each question must remain unanswered until more detailed plans are drawn up. In this section, a set of specifications is written down which serves to show in a concise way a definite machine based upon the best estimates now given in the text.

The reliability of these estimates varies with different parts of the machine. Some parts may be greatly influenced by future developments and may be realized by techniques different from those now contemplated and, hence, will involve a number of active elements quite different from the amounts listed below. The operation-time estimates are based upon small-scale experimental studies. Although factors affecting these times are taken into account insofar as possible in the extrapolation to the large-scale prototype, it is necessary to recognize that unforeseen characteristics of the prototype may require revision of the time estimates.

A tabular summary is presented where possible.

#### 1. Organization

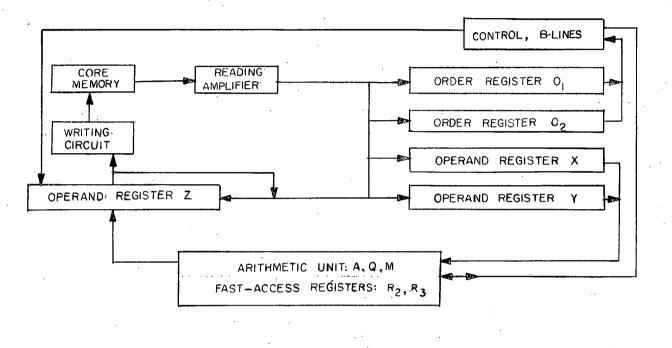

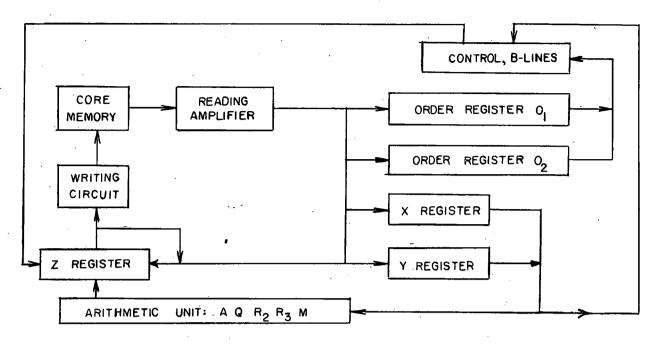

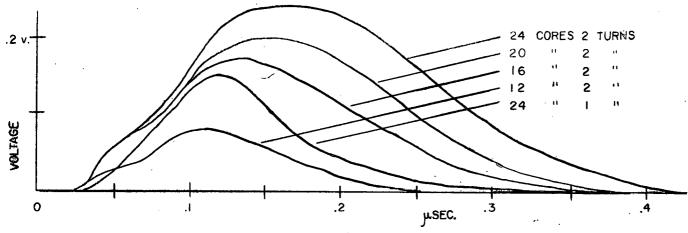

In accordance with the historical division of computing machines the machine may be considered to have: an arithmetic unit, a memory, a control and an input-output unit or units. However, the rather long memory access time (1.5  $\mu$ s) compared to the short addition time (0.32  $\mu$ s) requires temporary storage facilities intimately connected with the memory and the arithmetic unit. These will be called fast-access registers or fast-access memory. The interconnections are shown in block diagram form.

Reading from the memory is carried out at the same time the arithmetic unit is in operation. Thus, the memory may load order register  $0_1$  and operand register X during the time the arithmetic unit is performing a multiplication. Except for the brief period when the arithmetic unit is

ix

receiving or sending data to the fast-access registers, the arithmetic unit operates separately from the memory reading and writing operations. A part of the control called the advanced control arranges to keep registers  $0_1$ ,  $0_2$ , X, Y, and Z filled with data which the arithmetic unit is expected to need. Combinations of orders such as multiply and add help reduce accesses to the main memory.

Figure 1. Block Diagram

#### 2. Fast-Access Memory

| • • • | Non-shifting, | 52 bits each                                    |                                                                                        |

|-------|---------------|-------------------------------------------------|----------------------------------------------------------------------------------------|

|       | Non-shifting, | 52 bits each                                    |                                                                                        |

|       | Non-shifting, | 13 bits each                                    |                                                                                        |

|       | 52 bits       |                                                 |                                                                                        |

|       |               | Non-shifting,<br>Non-shifting,<br>Non-shifting, | Non-shifting, 52 bits each<br>Non-shifting, 52 bits each<br>Non-shifting, 13 bits each |

Each word is 1) 52-bit fixed point number

or 2) 42-bit floating point number, 10-bit exponent

or 3) four 13-bit control groups.

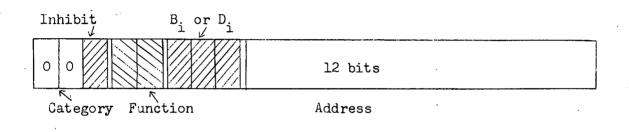

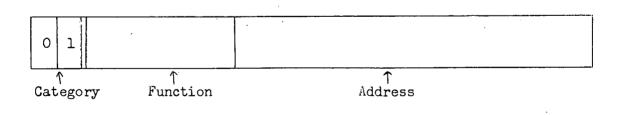

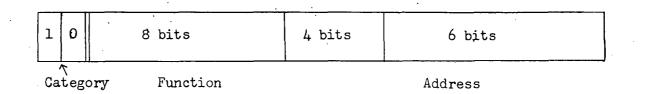

A short instruction has 7 bits for function, 4 bits for local fast register addressing, and 2 bits which are used for function or address bits.

A long instruction is a short instruction plus a 13-bit address.

| Access-time, fast memory to arithmetic unit | 0.05 µs |

|---------------------------------------------|---------|

| Number of orders outlined in text           | 100     |

#### Equipment for Fast-Access Memory

| Number of transistors | 2000 <u>+</u> 25% |

|-----------------------|-------------------|

| Number of diodes      | 8000 <u>+</u> 25% |

| Number of resistors   | 6300 <u>+</u> 30% |

#### 3. Arithmetic Unit

The arithmetic unit is characterized by an adder with carry completion sensing, separate carry register so that carries are not assimilated except when necessary and a multiplication scheme which senses two digits and shifts two places for each partial step. Recoding of the multiplier digits reduces the number of uses of the adder during multiplication to 52/3 = 17 on on the average.

#### Numbers

Number system Word length Addition

Number representation

Electrical bit representation Multiplication

Multiplication shifts Division

Overflow detection

Binary, parallel

52 bits

Separate carry register, carry completion sensing

2's complement, fixed and floating point

DC voltage

Reversed ternary multiplier recoding

Two at a time

Conventional non-restoring with remainder (type 1) or nonrestoring with standardization of partial remainders (type 2)

Available on all orders

xi

#### Registers

| Accumulator and quotient          | Shifting registers, 52 bits each |

|-----------------------------------|----------------------------------|

| Number register (M)               | Shifting register, 52 bits       |

| Operand registers $R_2$ and $R_3$ | Non-shifting, 52 bits each       |

## Fixed Point Operation Times without Access

| Addition without carry assimilation , .        | 0.19 µs <u>+</u> 10%                                         |

|------------------------------------------------|--------------------------------------------------------------|

| Addition with average carry assimilation $`$ . | 0.32 µs <u>+</u> 10%                                         |

| Multiplication without assimilation            | 3.8 μs average, <u>+</u> 10%<br>4.8 μs maximum, <u>+</u> 10% |

| Division, type 1 without assimilation          | 10-20 µs <u>+</u> 10%                                        |

| Division, type 2 without assimilation          | 7-14 µs <u>+</u> 10%                                         |

| Average carry assimilation                     | 0.13 µs <u>+</u> 10%                                         |

| Maximum carry assimilation                     | 0.67 µs <u>+</u> 10%                                         |

|                                                |                                                              |

#### Equipment Cost for Arithmetic Unit

| Number of transistors | 6,800 <u>+</u> 25%  |

|-----------------------|---------------------|

| Number of diodes      | 6,300 <u>+</u> 25%  |

| Number of resistors   | 11,500 <u>+</u> 30% |

#### 4. Control

The machine has an arithmetic control which forms instructions from  $0_1$ ,  $0_2$ , and the B-registers and properly sequences the arithmetic operations. The advanced control looks at instructions just ahead but not yet executed by the arithmetic unit and places additional data from the memory in  $0_1$ ,  $0_2$ , X or Y as necessary. Of course on conditional control transfer orders or other orders dependent upon calculations in process, the advanced control must wait for its information and no advantage is gained by the fast registers. Advanced control places operands in X, Y from addresses contained in  $0_1$  or  $0_2$  and then provides appropriate addresses to the arithmetic control to indicate that the operands are in X and Y.

A memory control to properly sequence the reading and writing from the memory and an input-output control are necessary.

| Equipm | ent | for | Contr | ols |

|--------|-----|-----|-------|-----|

|        |     |     |       |     |

| ·                    | No. Transistors   | <u>No. Diodes</u> | No. Resistors       |

|----------------------|-------------------|-------------------|---------------------|

| Arithmetic control   | 1200 <u>+</u> 30% | 4000 <u>+</u> 30% | 5000 <u>+</u> 50%   |

| Advanced Control     | 2400 <u>+</u> 30% | 8000 <u>+</u> 30% | 10,000 <u>+</u> 50% |

| Memory control       | 1000 <u>+</u> 40% | 3500 <u>+</u> 40% | 4000 <u>+</u> 60%   |

| Input-output control | 1000 <u>+</u> 40% | 3500 <u>+</u> 40% | 4000 <u>+</u> 60%   |

| Totals               | 5600 <u>+</u> 34% | 19,000 + 34%      | 23,000 + 54%        |

#### 5. Memory

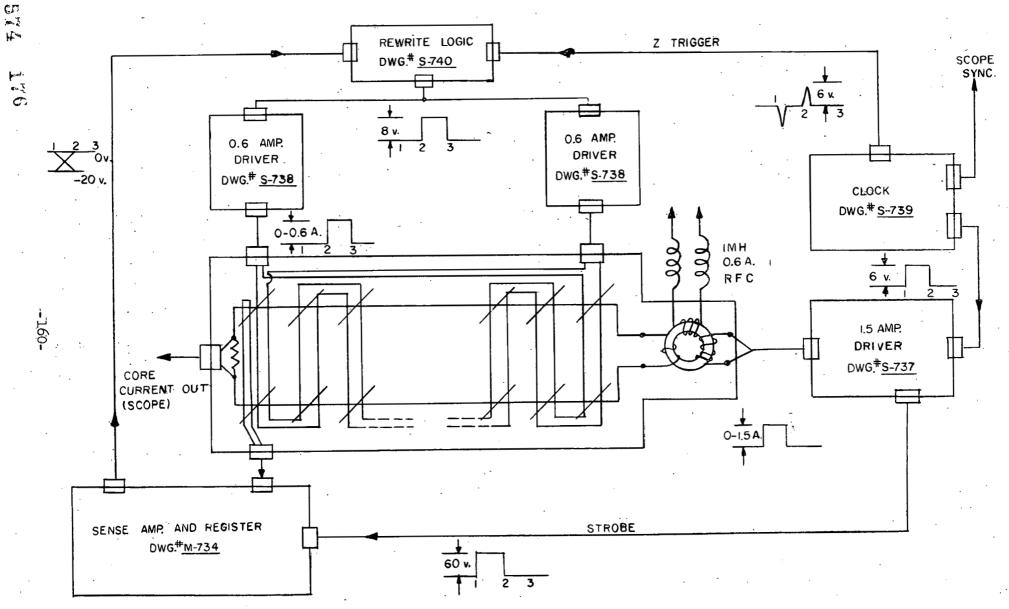

A core memory using the word-arrangement (or word addressing scheme) is favored because this produces the shortest access times with the conventional cores known to be available. In this addressing scheme, there is a smaller drive current restriction than in the coincident current system and hence the core turn-over time may be shortened.

#### Characteristics

Main internal random-access unit Random-access time Type of memory core Type of switch core 8192 words, 52 bits each

1.5 μs

General Ceramics S4,

size F-394

General Ceramics S5,

size F-394 By words

Type of addressing

#### Equipment for Memory

| Number of large vacuum tubes         | 300 <u>+</u> 20%  |

|--------------------------------------|-------------------|

| Number of small vacuum tubes         | 1000 <u>+</u> 20% |

| Number of transistors                | 1000 <u>+</u> 20% |

| Number of cores (two per bit stored) | 851,968           |

| Number of cores for switches         | 212,992           |

Auxiliary memories are listed under input-output.

xiii '

#### 6. Basic Circuits

The basic circuits use diffused-base transistors with provision to prevent the transistors from going into saturation at any time. This produces the shortest transistor switch time. The circuits are more complicated than the simplest circuits and require a larger number of parts. The number of tolerance problems is necessarily greater, and these are being checked with the Illiac. Diodes, of a particularly fast type, are also used as switching elements.

Circuits

Switching elements

Direct-coupled asynchronous Western Electric GF-45011 transistors, Qutronics Q5-250 or Q10-600 diodes or equivalent.

|                    | No. of<br>Transistors | No. of<br>Diodes | No. of<br>Resistors | Operation time<br><u>mµs</u> |

|--------------------|-----------------------|------------------|---------------------|------------------------------|

| Flipflop           | 4                     | 11               | 15                  | 30                           |

| NOT                | 2                     | 4                | 5                   | 15                           |

| AND                | 2                     | 0                | 3                   | 5:                           |

| OR                 | 2                     | 2                | 3                   | 5                            |

| Double gate        | 4.3                   | 1.2              | 8                   |                              |

| Half-Adder         | · 8                   | 6                | <b>ユ</b> 4          | 25                           |

| Complement Circuit | 6                     | 2                | 9                   | 10                           |

Although these circuits, and the logical developments giving rise to the operation times listed under the arithmetic unit, are direct-coupled, they are not under all conditions asynchronous. Chapter 5 is devoted to a discussion of this subject and a rigorous definition for asynchronism is presented. Although the more rigorous definition requires more care in application and more parts in most circuits, there are good prospects that it can be done and is worthwhile. Succeeding developments may adopt this new definition whenever possible.

xiv

#### 7. Input-Output

For balance only the fastest possible types of input-output would be appropriate. This includes only magnetic drums and the fastest magnetic tape units. These units are greatly affected by commercial developments and no specific items are listed.

#### Equipment for Off-Line Operation

Punched card equipment Punched paper tape equipment Card and paper tape to magnetic tape converters Fast printer

#### Equipment for On-Line Operation

Magnetic tape units with 30 or more channels per tape Magnetic drum, 50,000 words

Cathode ray tube display equipment

Switching elements need not have an operation time shorter than 1  $\mu$ s.

#### XV

#### CHAPTER 1

#### PROBLEMS REQUIRING FASTER COMPUTERS

#### 1.1 Introduction

Since the publication in 1946 of the fundamental report by A. W. Burks, H. H. Goldstine and J. von Neumann<sup>(1)</sup> a class of machines based directly on the ideas of this report have been built and put into operation. Other machines influenced in various degrees by this report have also been put into use. The experience obtained with these machines enables one to begin to discern the limitations of present-day computers in carrying out presently-formulated computational problems in various areas of applied mathematics, the physical sciences, and engineering as well as those computational problems arising in these and other fields whose solutions do not yet have a precise formulation in terms of arithmetic algorithms. Problems involving various types of partial or ordinary differential equations may be considered to be of the first class whereas problems involving a large degree of combinatorics and not necessarily arithmetic manipulation of various quantities may be said to belong to the second class.

It is the purpose of this chapter to discuss some problems of each type referred to above and to attempt to characterize them in terms of the requirements they impose on the memory, arithmetic unit and control of a computer. We shall be mainly concerned with the size and speed the first two of these organs must have.

In the analysis given below it will be assumed that for some problems, for example those which involve the solution of ordinary or partial differential equations, the time spent by present-day computers in obtaining the solution may be estimated by the formula:

T = F • Multiplication time • Number of Multiplications

where F is a number between one and ten, the multiplication time is the time

-1-

<sup>1. &</sup>quot;Preliminary Discussion of the Logical Design of an Electronic Computing Instrument," A. W. Burks, H. H. Goldstine, John von Neumann, Institute for Advanced Study (Princeton, N. J.) June 1946.

necessary for the arithmetic unit to multiply two numbers (exclusive of the time required to obtain these numbers from the memory), and the number of multiplications is the total number occurring in the problem.

Actually T, the time spent by a computer in solving a problem, is composed of four parts:

- the input-output time: the time spent in transferring the problem into and out of the machine,

- (2) the instruction access time: the time spent in transferring instructions from the memory to the control,

- (3) the operand access time: the time spent in transferring operands and partial results from the memory to the arithmetic unit and the time spent in the reverse process,

- (4) the arithmetic time: the time spent by the arithmetic unit in doing useful and necessary arithmetic.

For present-day computers these times are additive, although logically they need not be. Indeed, one possibility that many designers are exploring is the possibility of overlapping these times by building machines capable of performing a number of these tasks simultaneously, that is, in parallel.

As was pointed out by H. H. Goldstine, (2) the formula for T given above follows from the assumption that on the average, each multiplication can be imbedded in a sequence of (A+1) instructions consisting of one multiplication and A non-multiplicative instructions, each of which takes a time L to execute. The time to execute these instructions is then

$$t = M + AL + (A+1) (a_1 + a_0) = FM$$

where M is the multiplication time,  $a_i$  and  $a_o$  are the instruction and operand access-times respectively. Let

$$F = l + \frac{AL}{M} + \frac{(A+l)(a_i + a_o)}{M}$$

.

2. H. H. Goldstine: "Systematics of Automatic Electronic Computers," Proceedings of the Darmstadt Colloquium, October 1955.

. -2-

# 574 (18

We then have

$$T = Nt = FMN$$

where N is the number of multiplications. The estimates on the size of F are obtained by estimating the various quantities entering on the right-hand side of the equation for F.

Thus for a machine such as Illiac,

$a_{i} \approx \frac{1}{2} a_{o} \approx .025M$  $\frac{L}{M} = .08.$

Hence if A = 11 we have

F≈2.8 .

#### 1.2 Hyperbolic and Parabolic Partial Differential Equations

We begin the listing of problems which are beyond the capabilities of present-day computers with some time-dependent problems in hydrodynamics. These problems involve the solution of a system of hyperbolic partial differential equations in which the independent variables are one-, two- or three-space variables and time. If the integration is done in terms of Lagrange coordinates, the number of dependent variables is 2m + 1 where m is the number of spatial dimensions, since the Eulerian coordinates must be computed, the velocity field must be determined, and one thermodynamic variable in addition to the density must be calculated. Each of these 2m + 1 independent quantities must be evaluated as functions of the time.

The calculation can be arranged so that the value of any dependent variable at time  $t + \triangle t$  at certain values of the spatial coordinates is **determined** in terms of the values of some or all the dependent variables at time t. However, only the values of the dependent variables at time t at

019 574

spatial points in a region near the point of interest are needed in this calculation; that is, not all the data at time t is needed to calculate the values of a dependent variable at a single spatial point at the time  $t + \Delta t$ . This observation is important for the consideration of the memory requirements of a computer.

The size of the time-step (i.e. the size of  $\Delta t$ ) must be related to the size of the spatial mesh. Thus in a one-dimensional problem in which we evaluate the dependent variable at mesh points

$X = X_{a} + j \Delta X$  (j an integer)

we must have

$$C \Delta t \leq \Delta X$$

where C is the (variable) sound velocity.

If the problem is such that one would expect spatial variations in the dependent variables similar to those in the function

#### sin $2\pi kX$ ,

then one should have

$$2\pi k \Delta X \leq \frac{\pi}{2}$$

.

It is not unreasonable to require that the extent of each spatial variable be divided into between 10 and 100 mesh points; that is,

$$\frac{1}{10} \ge \Delta X \ge \frac{1}{100} \quad .$$

The amount of data which has to be stored at a given time is then

$$30 \leq D \leq 7 \cdot 10^6$$

,

where the lower limit holds for a one-dimensional problem with a 10-point spatial mesh and the upper limit holds for a three-dimensional problem with a cubical mesh having 100 points to a side.

# 574 (20

The number of multiplications involved in the calculation of the values of all the dependent variables at a mesh point depends on the number of dimensions. It may be assumed to be 30 for a one-dimensional problem, 50 for a two-dimensional one and 70 for a three-dimensional one. Hence, N, the total number of multiplications per time-step, will be

$$9 \cdot 10^2 \le N \le 4.9 \cdot 10^8$$

.

The computation time in seconds to perform the required calculations for one time-step with an existing computer with a multiplication time of  $5 \cdot 10^{-4}$  seconds and F = 2.5 is then

$$1.1 \le T \le 6 \cdot 10^5$$

.

If the computation is to be done for a number of time-steps M sufficient for signals to traverse the region under consideration K times, that is if

$$CM \Delta t \approx Km \Delta x$$

where m is the number of mesh points in each dimension, since  $C \Delta t \approx \Delta x$ , we would have

$M \simeq Km$ .

Hence for a single problem the computation time in seconds would be

$11K \leq t_c \leq 6K \cdot 10^7 .$

Quite often numerical surveys are made in which calculations are done again and again, each time with various parameters assigned different values.

It is clear that for moderate values of K the time required for a single calculation is excessive in the three-dimensional case. There are, of course, many one-dimensional problems in which the number of mesh points is considerably larger than 10 and K is of the order of 30. Thus even in a one-dimensional problem it is quite possible to have

$$t_{

m c} \approx 25$$

hours

for a single problem with an existing machine by taking m  $\approx 170$  and K = 30.

-5-

In two- and three-dimensional hydrodynamical problems done by use of Lagrangian coordinates there arises a difficulty in the calculation due to the fact that "particles" of the fluid which were originally neighbors do not remain neighbors. This implies that after some time-steps the calculation summarized above has to be interrupted and a new Lagrangian mesh has to be formed. If this process is to be done by the computer, the time estimates given above have to be increased. Moreover existing computers are not very efficient in performing combinatorial manipulations required in setting up the new Lagrangian net.

For parabolic differential equations the situation is much the same as that for hyperbolic ones with one very important difference. Instead of having the time-step linearly related to the spatial mesh size, we have

$$\Delta t \approx k(\Delta X)^2$$

.

This introduces another power of the number of mesh points in the expression for the number of multiplications required to integrate the equations for a given interval of time.

In summary it may be said that there are many problems involving hyperbolic and parabolic partial differential equations in which the total number of multiplications involved is between  $10^7$  and  $10^{11}$  and that in these problems 50,000 to 100,000 words of data are used. However the calculation may be so organized that relatively small amounts of this data are required at once. Therefore, it is not clear that a random access memory sufficient to hold 100,000 words of data is required.

#### 1.3 Elliptic Partial Differential Equations and Linear Equations

The solution of elliptic partial differential equations may be reduced to solving a set of linear equations:

$$Ax = b$$

for the n components of x where A is a given n x n matrix and the n components

574

of b are given. When such a system of linear equations arises from a partial differential equation, the dimensionality of the problem is related to the number of mesh points used in approximating the differential operators by difference operators. Values of n = 400 or greater are not uncommon.

The matrices A which arise in these problems usually have the property that the non-zero elements in any row of the matrix are relatively few in number. Moreover the location of these non-zero elements relative to the diagonal element is the same for each row. However the values of these elements will not be the same unless the coefficients of the differential equation are constants. For non-linear differential equations, these coefficients are not the same on successive iterations.

Because of these properties of the matrix A, the usual methods of solving the linear equations involve iteration processes. If we assume that 20 iterations of a matrix are required and that there are 10 non-zero elements in a given row of the 400 x 400 matrix we find that there are 80,000 multiplications required to find the solution of the problem once the coefficients of the matrix are known. In some problems these quantities may depend on their position in the matrix and on the approximate values of the x's. Therefore on each iteration the coefficients of the matrix A have to be evaluated. If the evaluation of each non-zero term involves 10 multiplications, we must perform 400  $\cdot$  10  $\cdot$  10 = 40,000 multiplications to evaluate the matrix on each iteration and hence 4.4  $\cdot$  10<sup>4</sup> multiplications per iteration or 8.8  $\cdot$  10<sup>5</sup> multiplications per 20 iterations.

Hence for a non-linear elliptic problem the number of multiplications is comparable to the number involved in hyperbolic and parabolic differential equations. However the amount of data that need be stored and manipulated may be much smaller than in the latter cases.

#### 1.4 Sorting and Meshing Problems

In scientific computations and in other problems one is quite often confronted with the need of comparing sets of quantities represented by numbers which are either stored in the machine or on some medium which may be read by the machine. One way of handling such problems is to order the data in some

-7-

fashion. Because this problem is very common it is worthwhile discussing it to see how time-consuming it can become and what factors affect the time involved in completing it.

Von Neumann and Goldstine have described a method for reducing a set of numbers (or a set of complexes of numbers) to a set ordered by size. The method consists of an application of a meshing process: two sets of ordered numbers are meshed as follows: let the first set of numbers be  $X_1, \ldots, X_n$  and the other set be  $Y_1, \ldots, Y_m$ . Then we form a single set

$$Z_1, Z_2, ..., Z_{n+m}$$

where

$$Z_k = X_i \text{ or } Y_j$$

where X, is the first of the remaining X's

$Y_j$  is the first of the remaining Y's, and k = i + j - l. The choice as to whether an X or Y is chosen depends on whether

$$X_i \ge Y_j$$

or

$$X_i < Y_j$$

.

Sorting is accomplished by successive meshing. Thus the numbers  $X_1, \ldots, X_n$  are first meshed, as if they were groups consisting of single elements, into n/2 groups of two elements:  $X_1, X_2; X_3, X_4; \ldots; X_{n-1}, X_n$ . These are then meshed into n/4 groups of four elements. This process continues until there are  $n/2^k$  groups of  $2^k$  elements each. If n is a power of 2, n =  $2^m$  the process stops when k = m.

The arithmetic being done in this problem consists of approximately

comparisons, for on every meshing operation there is a comparison for the

-8-

determination of each element of the new set. However, the time for completing the sorting cannot be estimated accurately by multiplying this quantity by the time for doing the arithmetical comparison. One must take account of the time required for "red tape" operations (the time required to locate and acquire the proper numbers for the comparison), and the time to determine where the winner of the comparison test is to be placed, and to store this number in the memory.

Thus, the time to complete the sorting will be of the form

# Kn log<sub>2</sub> n

where K is a time usually much greater than the time to perform a simple addition in a machine.

It is expected that in quite modest problems  $n \approx 1000 \approx 2^{10}$  and, hence, the time to sort is Kn  $\log_2 n \approx K \cdot 10^4$ . As a rough estimate we may take K to be 10 times the addition time of the computer and, hence,  $K = 4 \cdot 10^{-4}$  seconds for a machine such as Illiac. Thus, the sorting of 1000 pieces of data would take 4 seconds. Although this time itself may appear small, it may have to be repeated a very large number of times and may influence greatly the feasibility of doing a particular problem on a computer. If  $n \approx 10^6$ , the time estimate would be multiplied by  $2 \cdot 10^2$  and would require 8,000 seconds or 2 hours to carry out the task.

#### CHAPTER 2

#### REQUIREMENTS ON A VERY FAST COMPUTER

#### 2.1 Memory Capacity Requirements

In the discussion of problems described in sections 1.2 and 1.3 we have seen that the total number of multiplications may vary between 10<sup>7</sup> and 10<sup>11</sup> and that in some of these problems 50,000 or 100,000 words of data are used. However, not all of this data is needed at any one stage of the computation and therefore need not necessarily be stored entirely in the high-speed random-access memory. Indeed it is the purpose of this section to show that the use of a lower speed non-random-access memory (a "backup" memory) in conjunction with a faster but smaller memory does not involve a great percentage increase of computing time for those problems satisfying the following property:

The problem is such that if N words of data are in the high-speed memory we may then calculate N-k new words which replace the same number of words previously held. Thus in one sweep through the memory N-k words are calculated and these may be stored in positions previously occupied by other words. If N-k is as large as required by the problem, this process is repeated many times and the total time for the calculation is

$(N-k) \cdot n \cdot F \cdot M \cdot T = \mathcal{T}_{1}T$

where

n = the number of multiplications for each of the (N-k) words T = the number of times the memory is swept through,

If, however, N-k is not as large as required we must add to this the time necessary to load and unload the memory. Let us say that the time necessary to unload the high-speed memory is made up of two parts: (a) a time to get access to another memory,  $\ll$ , and (b) a time to read N-k words into this memory,  $(N-k)\mathcal{B}$ .

-10-

Thus unloading time is

Assuming that reading and writing in the latter memory take equal times and that we have to read N words from it in order to properly load the high-speed memory, we have as our loading time

$\alpha + N\beta$ .

Hence the total loading and unloading time is

$$2(\alpha + (N-k)\beta) + k\beta$$

.

The ratio of this time to the computation time per load in the memory

$$R = \frac{2(\alpha + (N-k)\beta) + k\beta}{(N-k)nFM}$$

$$R = \frac{2}{nFM} \left( \frac{\alpha + \beta \frac{k}{2}}{N-k} + \beta \right).$$

The total computation time is now

$(1 + R) \mathcal{T}_{1}T.$

Hence the ratio R is a measure of the cost of using a pair of memories instead of a single memory. We may write

Then

is

$$R = \frac{2}{nF} \left( \frac{\mathcal{A}_{1} + \frac{1}{2}}{N - k} + \mathcal{A}_{1} \right) = \frac{2}{nF} \left( \mathcal{A}_{1} + \frac{\mathcal{A}_{1}}{k} + \frac{\mathcal{A}_{1}}{2} \right) .$$

$\alpha/M = \alpha_1$

-11-

In this formula n, N, and k depend on the problem being solved and  $\alpha_1$  and  $\beta_1$  depend on the equipment being used. For a given problem we may estimate the size of high-speed memory N so that R is the order of 10%. The important thing to note is that the rate of change of R with N is a slowly-varying function beyond the value of 10%.

Goldstine<sup>(1)</sup> has shown that for a problem in hydrodynamics with time and two spatial variables for which 50,000 words of storage are needed, a core memory with room for 1750 words of data requires less than 10% of computing time for consulting the secondary memory when

> $M_{1} = 1700 \text{ or less}$  $B_{1} = .8 \text{ or less}$ k = 500n = 20F = 2.5

However, Goldstine did not consider the complications ensuing when slip-streams occur in the computations.

Suppose now we examine the question as to whether a random-access memory of 30,000-word capacity is needed.

In two- and three-dimensional hydrodynamics problems in which the quantities are time-dependent, the amount of data which has to be processed in one time-step will exceed this capacity by a factor which is at least between one and two and may be five. Therefore a backup memory will be needed in any case. We are thus dealing with the factor R and the question is what is the value of R for N  $\approx$  30,000 and say N  $\approx$  2,000.

1. H. H. Goldstine: "Systematics of Automatic Electronic Computers," Proceedings of the Darmstadt Colloquium, October, 1955.

-12-

ζ·)

Suppose we have a drum in which

$$\propto = 17000 \ \mu s = access-time to a word;$$

$\beta = 8 \ \mu s = read-time for a word;$

If then the multiplication time is assumed to be  $5 \,\mu s_{T}$

$$\mathcal{A}_{1} = 3400$$

$$\mathcal{B}_{1} = 1.6$$

$$R = \frac{2}{nF} \left( 1.6 + \frac{\frac{3400}{k} + .8}{\frac{N}{k} = 1} \right)$$

For k = 500

$$R = \frac{2}{nF} \left( 1.6 + \frac{7.6}{\frac{N}{500} - 1} \right)$$

$$R_{30000} = \frac{2}{nF} (1.7) = .068$$

$$R_{2000} = \frac{2}{nF} (3.6) = .144$$

where  $\frac{2}{nF} = .04$ , (F = 2.5, n = 20).

Hence the ratio of the times to do the same problem with a memory of  $32_{y}768$  words and one with 4768 words (2768 words of code being used) is

$$\frac{1.14}{1.07} = 1.07.$$

A 7% increase in time is gained by an almost eight-fold increase in size of memory.

## **=13**≓

029

For k = 1000 we have

$$R = \frac{2}{nF} \left( 1 \cdot 6 + \frac{4 \cdot 2}{\frac{N}{1000}} \right)$$

$$R_{30000} = \frac{2}{nF} \left( 1 \cdot 6 + \frac{.42}{3} \right) = \frac{2}{nF} \left( 1 \cdot 74 \right) = .07$$

$$R_{2000} = \frac{2}{nF} \left( 1 \cdot 6 + \frac{4 \cdot 2}{1} \right) = \frac{2}{nF} \left( 5 \cdot 8 \right) = .23$$

Here then we have a similar phenomenon. The ratio in times is

$$\frac{1.23}{1.07} = 1.15$$

a 15 speed-up being paid for by an almost eight-fold increase in size of memory. The doubling of the factor k, the amount of dead-weight data being carried in the transfers, is responsible for the change in time.

#### 2.2 The Class of Problems that can Use Backup Memories

It is clear from the discussion of parabolic and hyperbolic differential equations that these can be formulated so that they satisfy the assumption made in the previous section. That is, if N words of data are in the high-speed memory we may then calculate N-k new words which replace the same number of words previously held. Hence a backup memory can be used to good advantage on such problems.

It may also be used on algebraic problems arising in the solution of elliptic partial differential equations or integral equations. Such problems involve the solution of linear algebraic equations of the form

$$\mathbf{A}\mathbf{x} = \mathbf{b} = \mathbf{0} \tag{2.1}$$

$Ax = \lambda x = 0. \qquad (2.2)$

-14-

These problems may either be solved by iterative methods or by direct methods. The former are useful for large matrices in which many elements vanish. In such cases the (nxn) matrix A which may have  $n^2$  elements in reality is represented by many fewer elements and may be stored in a relatively modest high-speed memory. Thus for such cases where the matrix has relatively few non-zero elements and where an iterative method is used, that is the matrix A is not destroyed in the process of solution, there is no apparent need for a very high-capacity highspeed random-access memory.

Even when direct methods are used in solving linear equations such as equation (2.1) the price paid for using a modest-capacity low-access-time memory and a backup store in contrast to a high-capacity low-access time memory need not be excessive. This statement is justified as follows:

The direct method for solving equations (2.1) is the elimination method. Let us suppose that the matrix we are dealing with has n rows and n columns. It is to be reduced to a triangular matrix with the elements below the main diagonal zero by multiplying the rows by suitable numbers and subtracting them from subsequent ones.

We denote by p the capacity of the high-speed memory (for numerical storage) and write

n = pm

where we assume that m is an integer.

We propose to deal with m rows of the matrix A simultaneously. The first m rows of the (n+1) x n augmented matrix are read into the machine and as much elimination as can be done is done. The reduced data is then written on the drum. The next m rows of the original matrix are written into the machine. The first m rows are called back from the drum, used to reduce the second m rows, these partially reduced rows are further reduced into their final form and then written onto the drum. The third set of m rows is then called in and similar processes are applied. This continues until the whole matrix has been triangularized.

-15-

In this process the triangularized augmented matrix is written on the drum, that is

$$W = \frac{n(n+3)}{2}$$

numbers are written onto the drum and

$$R = (p-1) \frac{m}{2} (2n - m + 3) + (p-2) \frac{m}{2} (2n + 3 - 3m) + \dots \frac{m}{2} \left[ 2n + 3 - (2p-3)m \right]$$

numbers are read from the drum where

$$p = \frac{n}{m}$$

.

The time taken to perform W and R is the extra cost in time paid for by not having enough capacity in the high-speed memory.

$$R = \frac{m}{2} (2n+3) \sum_{r=1}^{p-1} (p-r) - \frac{m^2}{2} \sum_{r=1}^{p-1} (p-r)(2r-1) = \frac{m}{2} (2n+3) \frac{p(p-1)}{2} - \frac{m^2}{2} \frac{p(p-1)(2p-1)}{6}$$

$$R = \frac{n(n-m)}{4m} \left[ 2n+3 - \frac{(2n-m)}{3} \right]$$

$$R = \frac{n(n-m)}{4m} (\frac{4}{3}n + \frac{9+m}{3}) \approx \frac{n^3}{3m}$$

.

We may neglect W in comparison to R.

574 032

The number of multiplications involved in the triangularization of a matrix is to the same approximation

-16- . .

$\frac{n^3}{3}$

Hence the ratio of the reading from the drum time to the computation time is

$$\frac{1}{\mathrm{mF}} \beta_{1}$$

where we have assumed that we read in such large batches from the drum that the factor involving  $\alpha_1$  may be neglected.

If m is large enough this quantity may be made small so that the cost of not having a sufficiently high-capacity memory is not excessive even in this problem.

Even for sorting problems the use of a relatively small high-speed memory and a slower backup memory is not too costly in time. Let us suppose that we have a machine and a fast-access memory which is capable of sorting  $N_0$  numbers. Let us see how this may be used to sort N numbers which are originally stored on a drum. Let us write

$$N = rN_0$$

and assume that r is an integer.

We may sort the N numbers into r sets of N<sub>O</sub> numbers and involved in this is a reading of N numbers from the drum and a writing of these. This reading and writing can be done in blocks of N<sub>O</sub> numbers. The question arises as to what to do next. Now mesh the following numbers: A set of size K from the first N<sub>O</sub>, a set of the same size from second N<sub>O</sub>.... where

$$rK = N_0$$

In the process of sorting these numbers into  $N_O$  ordered numbers, one set of K numbers will be exhausted. Print out the first K sorted numbers and fill the space previously occupied by the exhausted set of K numbers with the next K numbers from the exhausted set. Thus the extra time involved in having a

-17-

574 (33)

backup store is the time required for two readings and writings of the data. The percentage increase in time is

$$\frac{2RN + 2WN}{KN \log_2 N} = \frac{2(R+W)}{K \log_2 N}$$

#### 2.3 Speed Requirements on the Memory

In section 1.1 it was stated that the quantity

$$F = 1 + A \frac{L}{M} + (A+1) \frac{a_i}{M} + (A+1) \frac{a_0}{M}$$

was one of the quantities determining the time for completing a computation and it was shown that for a machine such as Illiac this quantity was about 2.8 when  $\Lambda = 11$ .

With the present progress in circuitry it seems possible to design a computer with

$$M = 4 \ \mu s$$

$$L = .3 \ \mu s$$

$$a_0 = 1.5 \ \mu s$$

$$a_1 = .75 \ \mu s$$

(when orders are stored in pairs).

Hence

$$\frac{L}{M} = .075$$

$$\frac{a_{0}}{M} = .375$$

$$\frac{a_{1}}{M} = .188$$

574 (34

-18-

The corresponding figures for the Illiac are .08, .05 and .025 respectively. Hence we see that a machine with the same logical design as Illiac but using the latest circuit techniques would have a factor of

for A = 11. The corresponding figure for Illiac is

$$F = 1.08 + A(.16) = 2.8$$

that is, for the new machine the factor F would be three times larger. Since the time to do a computation is measured by F times the multiplication time the increase in the factor F vitiates in part the speed-up in multiplication time that can be achieved. If the multiplication time is decreased by a factor of 200, the total time to do a problem is decreased by a factor of only 67. This is because the terms  $\frac{a_0}{M}$  and  $\frac{a_1}{M}$  are so large for the present machine.

If F is to be the same for a machine with a multiply time of 4µs as for Illiac and if the logic of the two machines were to be the same we would have to have a word access-time from the memory of about .15µs, that is, ten times faster than seems possible with present techniques involving core memories.

It is the purpose of the next chapter to discuss methods of reorganizing the computer and adding extra equipment so that a reasonable fraction of this factor of three in loss of speed is recaptured. The computers there proposed manage to recoup this factor on some problems. They are no slower than sequential machines on other problems and therefore at the worst would be at least sixty times as fast as Illiac.

#### 2.4 Numerical Requirements on Word Length

The word length for a given machine is influenced by arithmetic and organizational considerations. Mainly because of the former it is proposed to use a word length of 52 bits. There are two major arguments for this based on fixed point and floating point arithmetic respectively.

If a floating point number is represented as an exponent and fractional part packed into one word, then the word length should be sufficient to maintain accuracy in floating point arithmetic. A 42-bit fractional part seems to be

-19-

just adequate for this purpose. It is therefore proposed to use 10 bits as an exponent for floating point numbers and 42 bits as the fractional part. We shall discuss floating point arithmetic further in subsequent sections of this chapter.

Even with fixed point arithmetic there is an argument for increasing the word length for the representation of numbers over that used in computers such as Illiac. In essence this is the following: With faster computers larger problems are done in which more computations are carried out and in which round-off plays a larger role. Hence more guard digits are needed. An estimate of how many additional digits are needed may be obtained as follows:

Von Neumann and Goldstine<sup>(2)</sup> have shown that in inverting a matrix the limiting value of n, the size of the matrix, for which the results are accurate, is related to the number base  $\beta$  and the number of places carried, s, by the inequality

$$n < .15 \beta^{s/4}$$

.

Further the amount of time needed to invert a matrix is proportional to the number of multiplications, that is,  $n^3$ .

Hence for a machine about 128 times faster than Illiac, we should be able to invert a matrix of size  $2^{7/3}$  n in the same time as that with which Illiac deals with an n<sup>th</sup> order matrix. If the results for this larger matrix are to be as accurate as those obtained from the Illiac on the smaller matrix we must have the number of bits carried on the fast machine, s', given by

$$s' = s + 4 \left(\frac{7}{3}\right) \approx 50.$$

The problem seems to be the most stringent algebraic one for determining the number of bits needed.

<sup>2.</sup> H. H. Goldstine and J. von Neumann, "Numerical Inverting of Matrices of High Order," Bulletin American Mathematical Society, vol. 53, no. 11, pp. 1021-1099, November 1947.

#### 2.5 Floating Point Arithmetic

Because many problems of the complexity and magnitude requiring a computer of the type discussed in this report are difficult to scale without some preliminary calculations, it seems worthwhile to have automatic facilities for floating point operation incorporated into the computer. However, as has been pointed out by Metropolis<sup>(3)</sup> it is not clear that the usual methods for performing floating point operations are the best ones that can be used. Numerical experiments are being planned at the Digital Computer Laboratory to help determine a reasonable set of rules for the automatic floating point operations to be incorporated into the computer.

The difficulty in using floating point arithmetic arises because the usual automatic floating point operations give no indication of relative error of the fractional part of the machine representation of numbers and indeed do not preserve relative errors in a computation.

Real numbers may be written as

$$x = 2^{x_e} x_f$$

where  $x_e$  is the exponent of the number and  $x_f$  is the fractional part. A computer represents the number by

$$\bar{\mathbf{x}} = 2^{e} \bar{\mathbf{x}}_{f}$$

where

$$\bar{\mathbf{x}}_{\mathbf{f}} = \mathbf{x}_{\mathbf{f}} + \epsilon_{\mathbf{x}}$$

$\epsilon_x' x_f \approx \epsilon_x' x_f$  is then the relative error in the fractional part of the number and

$$\overline{\mathbf{x}} = 2^{\mathbf{x}} (\mathbf{x}_{\mathbf{f}} + \boldsymbol{\epsilon}_{\mathbf{x}}).$$

3. N.Metropolis: "Floating Point Arithmetic," to appear in IRE Transactions on Electronic Computers.

The quantities  $x_e$  and  $x_f$  are not uniquely determined by x. For fixed point operation the computer user is required to restrict x so that

$-1 \le x < 1$ ,

$x_{o} = 0.$

and then

This implies that a problem is scaled before the computer is used. In some cases this is done incorrectly in which case overflow occurs in the computation. Overflow may occur in accumulating a sum or in an improper division (one in which the denominator is less than the numerator).

To avoid scaling difficulties floating point operations are used. In these the restriction is made that

$$\frac{1}{2} \leq x_f < 1,$$

which fixes x\_.

The problem in doing arithmetic is to keep track of the size of  $\epsilon_x$  as compared to the size of  $x_f$ . The  $\epsilon_x$  accrue during arithmetic operations and their determination is complicated. The initial error made by inserting the fractional part of a number in a machine is bounded by  $\delta = 2^{-S}$  where s is the number of binary places to which numbers are stored (or one more). Then

$$|\epsilon_{\mathbf{x}}| \leq \delta$$

and

$$|\frac{\mathcal{E}_{\mathbf{x}}}{\mathbf{x}_{\mathbf{f}}}| = \frac{\delta}{\mathbf{x}_{\mathbf{f}}} \approx \frac{\delta}{\overline{\mathbf{x}}_{\mathbf{f}}}$$

when we may neglect  $\frac{\delta \mathcal{E}_{\mathbf{x}}}{\mathbf{x}_{\mathbf{f}}}$ .

In any computation difficulties ensue when  $x_f$  and  $\epsilon_x$  are of the same order of magnitude. In fixed point work this can be sensed from the magnitude of  $\bar{x}_f$ , that is, a computation in which too small values of  $\bar{x}_f \approx k \delta$ , where k is a "small" integer, occur, the  $\bar{x}_f$  have to be treated with great care. In floating point the ability to sense troublesome  $\bar{x}_f$  is lost, since all  $\bar{x}_f$  are made to lie between 1/2 and 1.

That  $x_f$  and  $\epsilon_x$  may become of the same order of magnitude is clear from the subtraction process. Suppose we have two standardized numbers  $\bar{x}$ and  $\bar{y}$  with  $x_p \ge y_p$  then one could form the difference between these as

$$\overline{\mathbf{d}} = \overline{\mathbf{x}} - \overline{\mathbf{y}} = 2^{\mathbf{x}_e - \mathbf{p}} \begin{bmatrix} 2^{\mathbf{p}} (\mathbf{x}_f - 2^{\mathbf{y}_e - \mathbf{x}_e} \mathbf{y}_f) + \epsilon_d \end{bmatrix}$$

where

$$\epsilon_{d} = 2^{p} (\epsilon_{x} - 2^{y} e^{-x} e^{-x}) + \epsilon',$$

and  $\epsilon'$  is a rounding error. Now it is quite possible that although  $x_f$  and  $y_f$  are large compared to  $\epsilon_x$  and  $\epsilon_y$  respectively the quantity  $(x_f - 2 e^{-x_e} y_f)$  is of the order of  $\epsilon_d$ . The exponent p occurring in the above measures the number of "significant" zeros in the difference. Metropolis<sup>(3)</sup> suggests storing p as zeros in front of the first non-zero digits of  $\bar{d}_f$ , that is, he proposes not to automatically standardize numbers of the arithmetic operations.

Then rules for performing arithmetic have to be provided. A provisional incomplete set of rules (4) is:

<u>Addition and Subtraction:</u> Position number with smaller exponent by shifting it to the right. Carry and addition or subtraction. If overflow occurs shift one place right and adjust exponent. Never shift to the left and standardize the result.

- 3. N. Metropolis: "Floating Point Arithmetic", to appear in I.R.E. Trans. on Electronic Computers.

- 4. These rules are based on those given by Metropolis in (3). They differ from his in the multiplication process as is discussed in the text. The Digital Computer Laboratory is very grateful to Dr. N. Metropolis for supplying a preprint of his paper to that Laboratory.

Multiplication: Given

$$\bar{\mathbf{x}} = 2^{e} \bar{\mathbf{x}}_{f}$$

$\bar{\mathbf{y}} = 2^{e} \bar{\mathbf{y}}_{f}$

÷.,

Y

and also  $\bar{x}_{f} \geq \bar{y}_{f}$ . Form

$$\overline{xy} = 2^{x} e^{-p+y} e^{(2^{p}\overline{x}_{f}\overline{y}_{f})_{R}}$$

$$= 2^{x} e^{+y} e^{-p} \left[ \left( 2^{p} (x_{f} + \epsilon_{x}) (y_{f} + \epsilon_{y}) \right) + \epsilon^{1} \right]$$

$$\approx 2^{x} e^{+y} e^{-p} (2^{p} x_{f} y_{f} + 2^{p} \epsilon_{x} y_{f} + 2^{p} \epsilon_{y} x_{f} + \epsilon^{1})$$

where p is determined so that

$$\frac{1}{2} \leq 2^p \, \bar{\mathbf{x}}_{\mathbf{f}} < 1,$$

the relative error is

$$\frac{2^{p} \epsilon_{\mathbf{x}} \mathbf{y}_{\mathbf{f}} + 2^{p} \epsilon_{\mathbf{y}} \mathbf{x}_{\mathbf{f}} + \epsilon^{\mathbf{i}}}{2^{p} \mathbf{x}_{\mathbf{f}} \mathbf{y}_{\mathbf{f}}} \approx \frac{2^{p} \epsilon_{\mathbf{x}} \overline{\mathbf{y}}_{\mathbf{f}} + 2^{p} \epsilon_{\mathbf{y}} \overline{\mathbf{x}}_{\mathbf{f}} + \epsilon^{\mathbf{i}}}{2^{p} \overline{\mathbf{x}}_{\mathbf{f}} \overline{\mathbf{y}}_{\mathbf{f}}}.$$

In order that the round-off process will not contribute appreciably to the error in the product on a single multiplication, we require

$$\frac{2^{p} \epsilon_{y} \bar{x}_{f}}{2^{p} \bar{x}_{f} \bar{y}_{f}} > \frac{\epsilon'}{2^{p} \bar{x}_{f} \bar{y}_{f}}$$

This requirement states that the dominant error in the product be larger than the round-off error, that is, the size of the relative error in the product will be that in the factors. Now  $2^p \bar{x}_f$  is made to lie between 1/2 and 1 by the definition of p. Hence

$\frac{1}{2} \epsilon_{y} \leq 2^{p} \bar{x}_{f} \epsilon_{y} \leq \epsilon_{y}$

Thus if  $\epsilon_y$  is of the order of  $\epsilon^{y}$  this criterion will be violated. Note that  $\epsilon_y$  will become of the order of  $\epsilon^{y}$  after a sequence of multiplications of this sort since it gets decreased in each multiplication.

Muller has suggested that a product be formed as

This has the effect of increasing p by 1 and now achieves the desired result since it replaces the above inequality by

$\overline{xy} = 2^{x_e^{+y_e^{-p-1}}} \left[ 2(2^p \ \overline{x}_f \ \overline{y}_f) \right]_p .$

$$\epsilon_{y} \leq 2^{p+1} \bar{x}_{f} \epsilon_{y} \leq 2^{e} y$$

but the relative error is unaltered.

Division: The rules for this operation given by Metropolis for forming  $\bar{x}/\bar{y}$  are:

(1) Shift  $\bar{x}$  to the right if necessary until  $|\bar{x}| < |\bar{y}|$ .

(2) Standardize  $\overline{y}$ .

(3) Form the rounded quotient of the resulting numbers. These rules do not have the property that

$$\epsilon \left( \tilde{\mathbf{x}} / \tilde{\mathbf{y}} \right)_{\mathbf{f}} \approx \frac{\epsilon_{\mathbf{x}}}{\mathbf{x}_{\mathbf{f}}} - \frac{\epsilon_{\mathbf{y}}}{\mathbf{y}_{\mathbf{f}}}$$

and involve both right and left shifts. For these reasons numerical experiments are being planned to see if a better set of rules for division can be evolved.

-25-

#### CHAPTER 3

#### PROPOSED ORGANIZATION OF THE COMPUTER

#### 3.1 Introduction

The present state of computer components and computer circuits is such that it seems possible to build an arithmetic unit with a multiplication time  ${}^{(1)}$  M = 3.5 µs and an addition time L = .35 µs. The description of an arithmetic unit with these characteristic times will be found in Chapter 8. These times are between 100 and 200 times faster than the corresponding times of current computers such as Illiac.

However, corresponding progress in speeding up the memory access=time has not been made. A large-capacity random-access memory will probably use magnetic cores and if these are put together in the form of a "word-arrangement" memory, (cf. Chapter 6) the access-time per word would be a =  $1.5 \ \mu$ s. This seems to be the shortest access-time possible for a core memory using presently available cores. This access-time is about 18 times as fast as the accesstime of Illiac's memory. Thus progress in memories lags by a factor of between five and ten behind progress in arithmetic and control units.

For this reason the present-day machine designer must reconsider the organization of the computer and see if it is possible to mitigate the effects of the unbalance between the speeds of the arithmetic unit and the memory. It is the purpose of this chapter to discuss various methods by which this can be done and to propose machine organizations which incorporate these methods.

# 3.2 <u>A Design Criterion</u>(2)

The designer may have to choose one from many alternative designs each with a different number of switching elements and a different speed of

1. The best present estimates of the average multiplication time places it between  $3.5 \ \mu s$  and  $4 \ \mu s$ . This chapter is based on the lower figure. Its conclusion would not be materially altered if the higher figure were used.

2. It is proposed to apply this criterion in later work.

. **-**26-

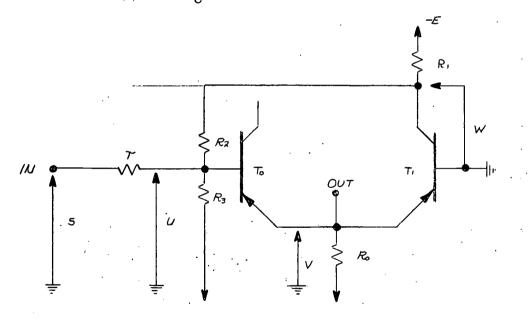

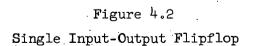

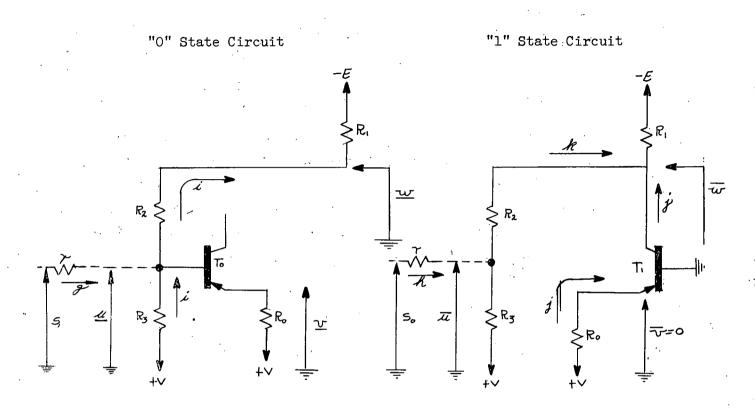

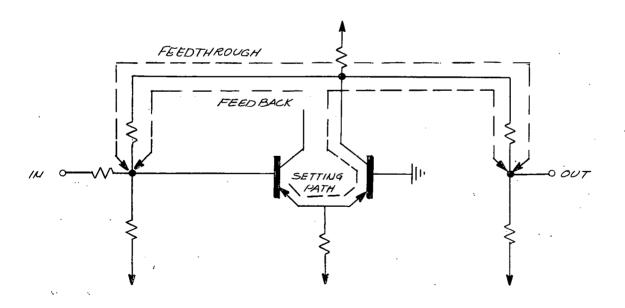

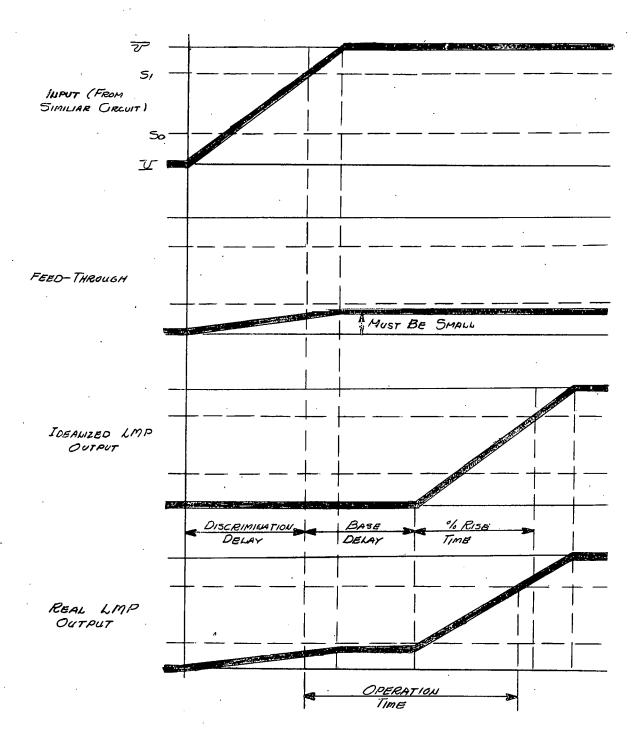

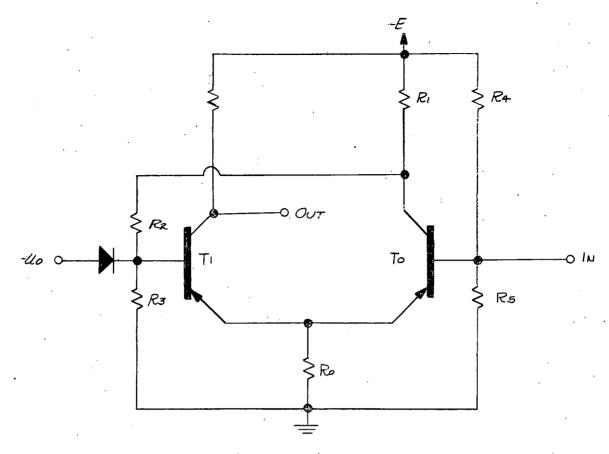

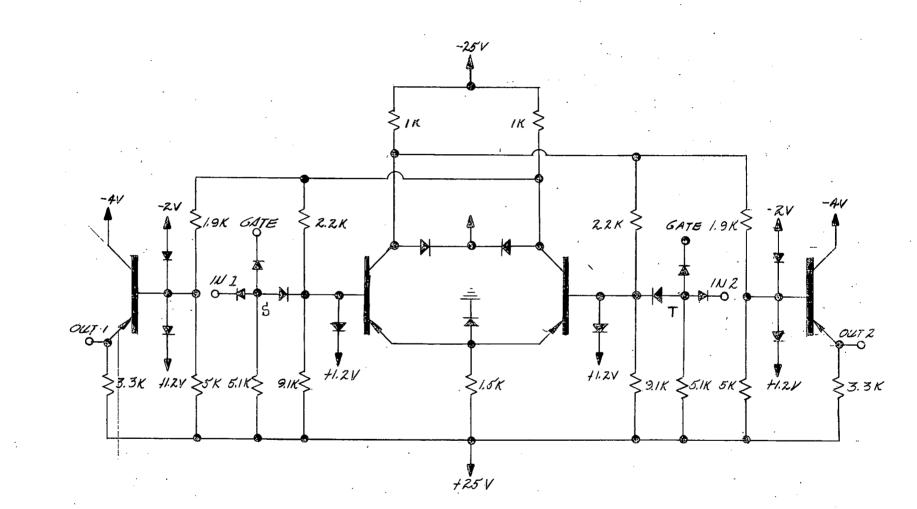

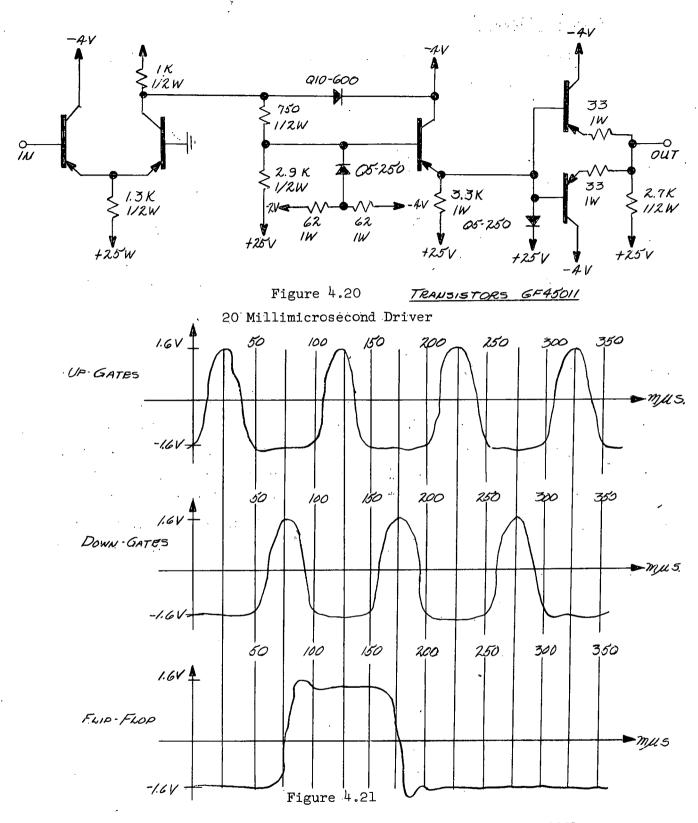

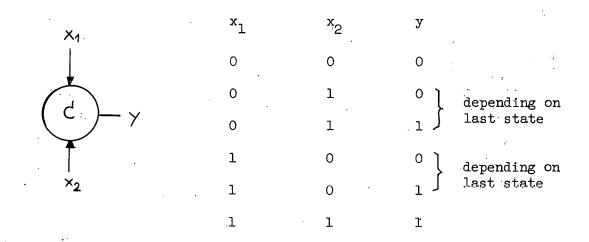

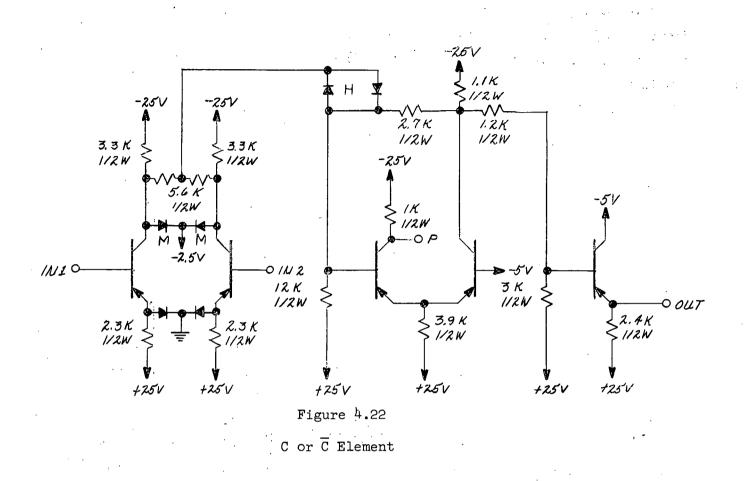

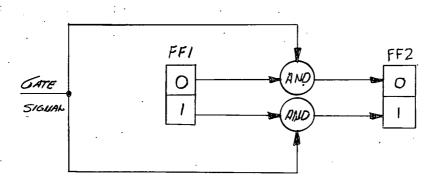

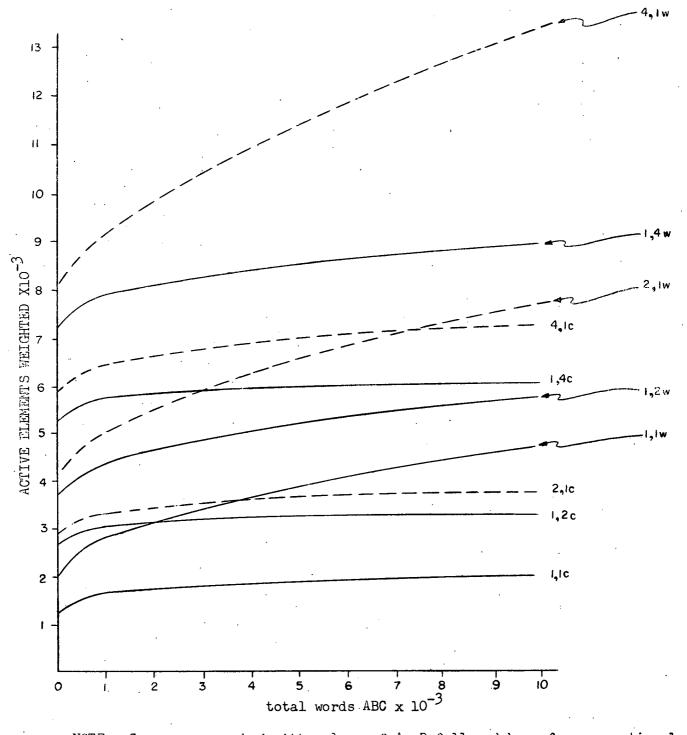

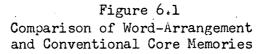

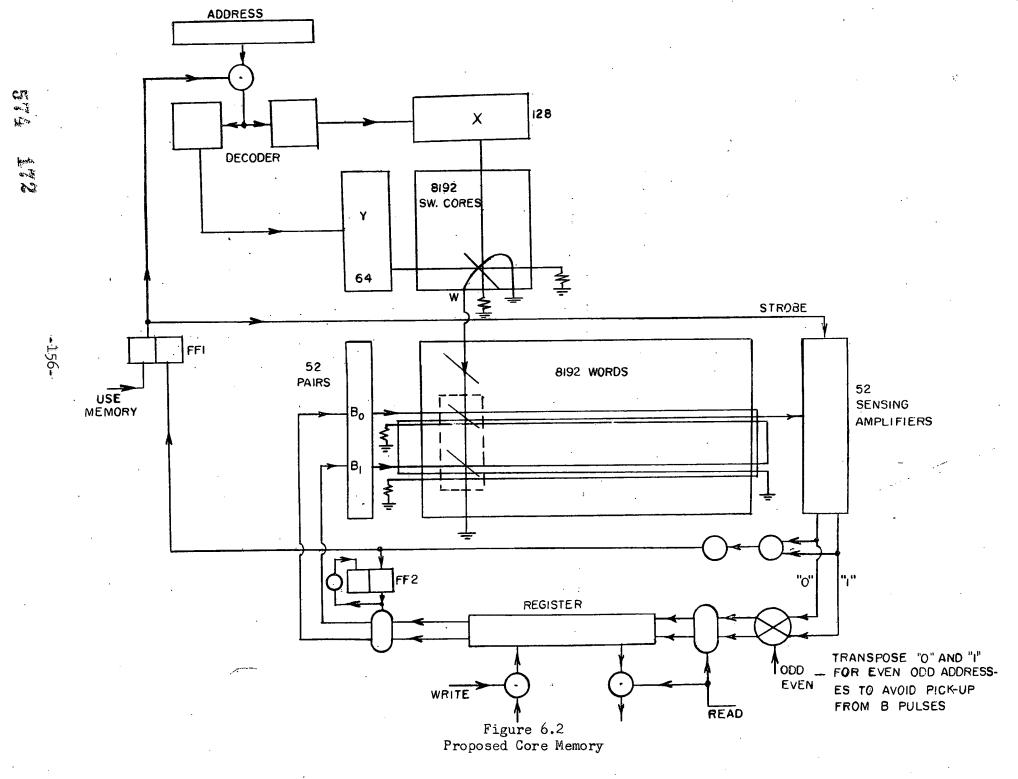

computation. The latter quantity may depend on the problem posed to the machine. If for a given class of problems the speed of computation can be estimated sufficiently accurately then the criterion discussed below may be used to choose between various designs. It should be noted that increased complexity may produce a slowing down of each individual element because the speed of an element is usually proportional to the number of elements to which it is connected.